2025年12月24日 09:43:39 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:11

关于芯片内部时钟、外部时钟晶振与外设总线的关系,晶诺威科技解释如下:

芯片内部时钟(Internal Clock Signal)

芯片内部时钟可能不稳定,一个是不同芯片有误差,同时随着温度的变化,对内部时钟的精度影响很大。芯片内部时钟精度本身也很差,仅为百分之几。

芯片外部时钟(External Clock Signal)

外部时钟通常指由外部无源晶振(石英晶体谐振器)或有源晶振(石英晶体振荡器)提供的高精度时钟,其频率精度可达百万级(ppm)甚至更高(ppb)。

晶振精度ppm值:

例如:±10ppm,意味着晶振输出频率与理论频率相差10个百万分之一。

通常,芯片的时钟电路有两个信号端口,一个是输出out,另一个是输入in。端口out专为外部无源晶振起振使用。如果采用为有源晶振,则有源晶振的信号输出脚(通常为三号脚)直接连接芯片的信号输入in即可。

以常见的STM32时钟为例

HSE (High Speed External Clock Signal)高速外部时钟信号

HSI (High Speed Internal Clock Signal)高速内部时钟信号

高速时钟信号通常指频率单位为MHz的信号,如4MHz、8MHz、12MHz、16MHz等。

LSE (Low Speed External Clock Signal)低速外部时钟信号

LSI (Low Speed Internal Clock Signal)低速内部时钟信号

低速时钟信号通常指频率32.768KHz,也有人粗略的称之为32KHz,其主要作用是实时时钟(RTC)。

外设总线

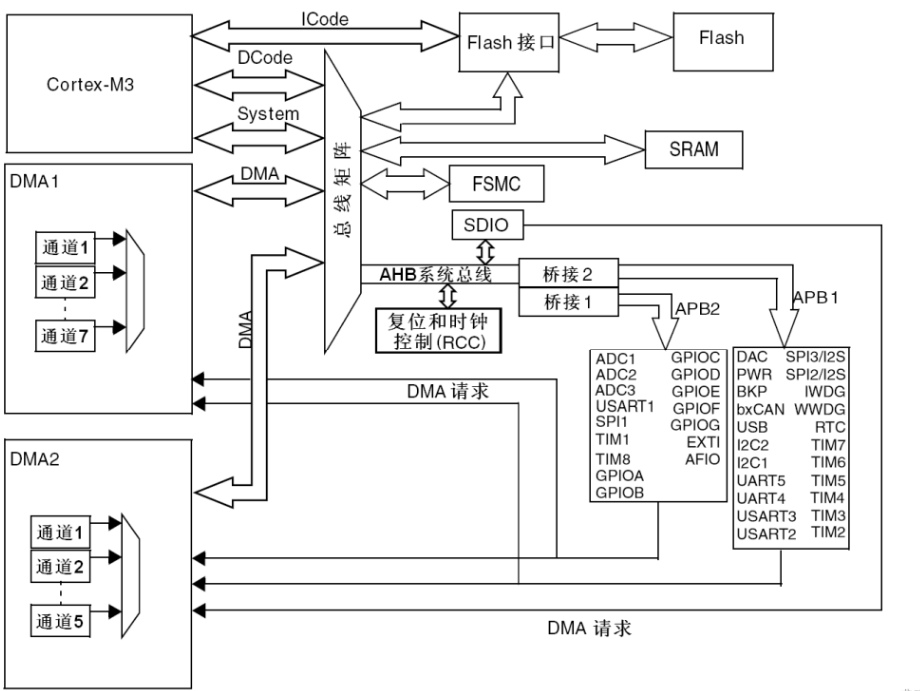

总线是一种用于连接处理器、内存和外设的通信架构,它可以传输数据和控制信号。计算机中的三大总线由数据总线、地址总线和控制总线组成,它们用于处理器与内存和外设之间的数据传输、地址定位和控制信号传递。在STM32中,AHB、APB1和APB2都属于处理器和外设之间的数据传输和控制信号传递。

AHB总线连接总线矩阵,同时通过2个APB桥连接APB1和APB2,AHB总线速度为72Mhz,APB2总线速度也是72Mhz,APB1总线速度只能是36Mhz。这三个总线上面挂载了STM32内部绝大部分外设。

AHB=Advanced High Performance Bus,译作高级高性能总线。AHB用于高性能模块(如CPU、DMA和DSP等),用于连接处理器核心、高速存储器和高带宽外设。

APB=Advanced Peripheral Bus,译作高级外设总线。

APB1总线上连接了一些低速外设和模块,如串口、I2C、SPI等。APB2总线上则连接了一些高速外设和模块,如定时器、串行接口、USB等。