2025年12月28日 08:54:31 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:8

EMC全称Electro Magnetic Compatibility,指设备或系统在其电磁环境中能正常工作,且不对该环境中任何事物构成不能承受的电磁骚扰的能力。EMC是评价电子产品质量的一个重要指标。

从广义上讲,EMC测试的具体项目包括以下两个大项:

(1)EMI(Electro-Magnetic Interference)—电磁干扰测试

此测试之目的为:检测电器产品所产生的电磁辐射对人体、公共电网以及其他正常工作之电器产品的影响。

(2)EMS(Electro-Magnetic Susceptibility)—电磁抗扰度测试

此测试之目的为:检测电器产品能否在电磁环境中稳定工作,不受影响。

再划分到小点,这两个大项的具体项目以及各自项目对应的常用测试标准如下:

其中EMI包括:

(1)辐射骚扰测试(RE)—测试标准:EN55022

(2)传导骚扰测试(CE)—测试标准:EN55022

(3)谐波电流测试(Harmonic)—测试标准:EN61000-3-2

(4)电压变化与闪烁测试(Flicker)—测试标准:EN61000-3-3

EMS包括:

(1)静电放电抗扰度测试(ESD)—测试标准:EN6100-4-2

(2)射频电磁场辐射抗扰度(RS)—测试标准:EN61000-4-3

(3)射频场感应的传导骚扰抗扰度(CS)—测试标准:EN61000-4-6

(4)电快速瞬变脉冲群抗扰度测试(EFT)—测试标准:EN61000-4-4

(5)浪涌(冲击)抗扰度(SURGE)—测试标准:EN61000-4-5

(6)电压暂降,短时中断和电压变化抗扰度测试(DIP)—测试标准:EN61000-4-11

(7)工频磁场抗扰度测试(PFMF)—测试标准:EN61000-4-8

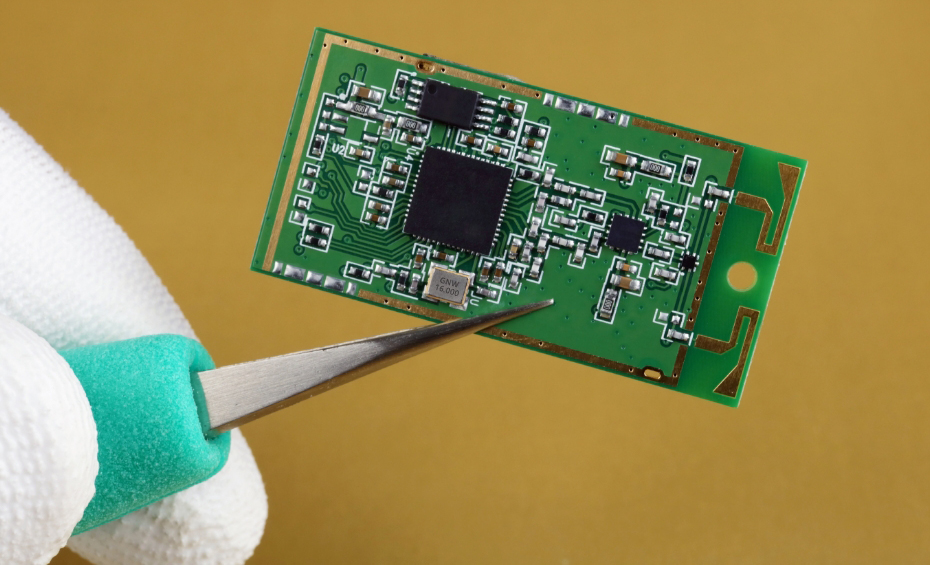

在电路板上电后,若作为频率器件的晶振周边存在较强杂散电磁信号时,会直接导致晶振输出频率受到干扰,引发频率偏移,严重时影响电路板正常工作。因此晶振本身具备抗电磁干扰能力也是晶振品质的一个重要特性。另外,在电路板布线时需要注意:

1、晶振尽量靠近芯片,走线短且直。

2、晶振引出的两根时钟信号线也要短,防止形成发射天线。

3、尽量设计晶振位于远离电磁波干扰区域,如远离电源,天线等器件。

4、晶振下方不要走线,走线过程不能隔断,不要过孔换层。

5、屏蔽晶振,接地脚接地。

了解更多晶振相关资讯,请点击晶诺威以下链接: