2025年12月28日 08:55:47 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:9

作为频率电子元器件,晶振设计是电子产品中电路元件和器件的支撑件,它提供电路元件和器件之间的电气连接。目前电子产品日趋小型化,PCB的密度也随之越来越高。PCB设计对抗干扰能性影响很大,因此在进行PCB设计时,首先,要考虑PCB尺寸大小。PCB尺寸过大时,印制线条长,阻抗增加,抗噪声能力下降,成本也增加; 若过小,则散热不好,且邻近线条易受干扰。在确定PCB尺寸后。再确定特殊元件的位置。最后,根据电路的功能单元,对电路的全部进行布局。

时钟源通常是系统中最严重的EMI辐射源,如果接长线,其结果是长线就成了天线,这在很多应用中是不准许的,所有时钟源都必须尽量靠近相关器件。必要时用多个时钟源。晶振和芯片的距离一般要尽量靠近。即使所采用的是有源晶振,也不能输出接长线。

那么,提供重要时钟信号的晶振应该设计在哪一层较好呢? 晶诺威科技建议如下:

1、晶振下不可走线,电路尽量靠近芯片端。

2、路径尽量短,与其他信号需20mil间距,使用接地方式与其他信号隔离。

3、晶振底下尽量不要走线。如果实在要走线的话,不能走线进晶振引脚周围50mil之内。尤其避免高速讯号。

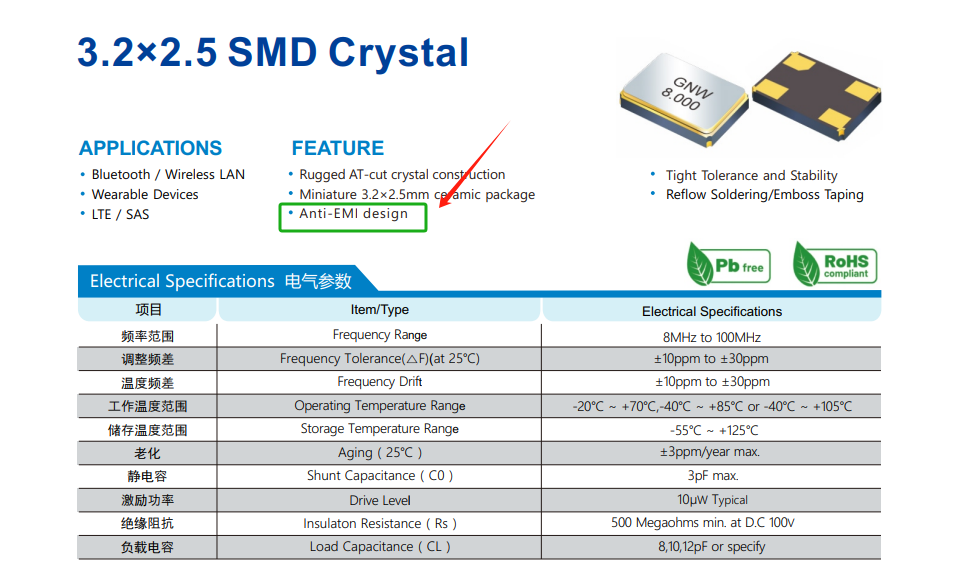

另外,晶诺威科技针对电磁干扰(EMI)问题,研发了具有抗干扰特性的晶振。该类晶振通过采用特殊的电路设计、材料选择及制造工艺,有效提高了自身的抗电磁干扰能力。

(晶诺威科技产抗EMI晶振)

总结

晶振信号线尽可能短,需要包地(因为有噪声,目的就是怕信号线影响其它元件,或者避免别的元件影响到晶振的频率信号)。尽可能不穿孔,因为一个过孔会有0.5pF的寄生电容,另外,走线粗细要一致。

另外,为了避免晶振受到PCB边缘的干扰,通常可以采取以下措施:将晶振放置在离PCB边缘一定距离的位置,以减少外界干扰的影响;在晶振周围设置合适的屏蔽罩,以减少外界电磁辐射的影响;考虑机械固定的问题,避免晶振受到机械振动的影响;合理规划晶振的布局,避免与其他元器件产生电磁干扰;合理规划散热措施,以减少温度变化对晶振的影响。

了解更多晶振相关资讯,请点击晶诺威以下链接: