2025年12月31日 08:06:02 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:10

常见差分晶振的差分逻辑信号类型及特点介绍如下:

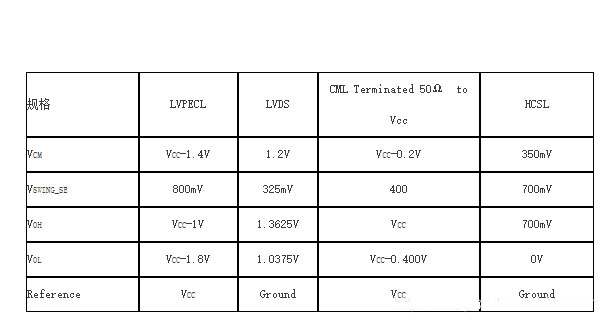

每个可用的时钟逻辑类型(LVPECL、HCSL、CML和LVDS)使用的共模电压和摆幅电平低于下一个时钟逻辑类型,在任何给定的系统设计中,必须设计驱动器侧和接收器侧之间的时钟逻辑转换。通过在它们之间增加衰减电阻和偏置电路来将一个差分时钟转换为其他类型的差分逻辑,来衰减摆幅电平并重新偏置共模输入接收器。

各差分时钟逻辑的输入/输出结构

在设计逻辑转换电路之前,需要检查每种逻辑类型(LVPECL,HCSL,CML和LVDS的输入/输出结构),因为每种逻辑类型具有不同的共模电压和摆幅电平。

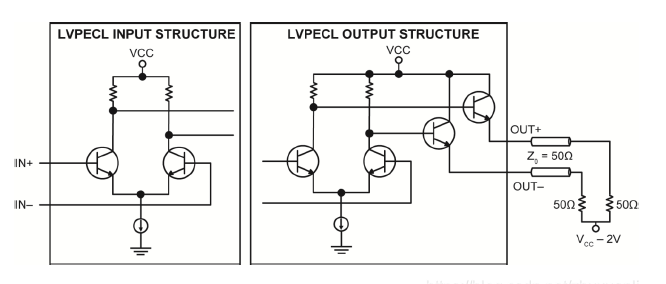

低压,正参考,发射极耦合逻辑(LVPECL)

低压,正参考,射极耦合逻辑(LVPECL)源自发射极耦合逻辑(ECL),采用正电源。

LVPECL输入是具有高输入阻抗的电流开关差分对。输入共模电压应约为Vcc-1.3V,用于具有内部自偏置或外部偏置的工作余量。

LVPECL输出由差分对放大器组成,驱动一对射极跟随器(或开放发射器)。输出射极跟随器应在“有效”区域内工作,始终具有直流电流。OUT +的输出引脚 和OUT-通常连接到差分传输线(Z0 =100Ω)或单端传输线(Z0 =50Ω)用于阻抗匹配,LVPECL输出的正确终端为50Ω至Vcc-2V和OUT + / OUT-通常为Vcc-1.3V,导致近似的直流电流为14mA。

另一种终止LVPECL输出的方法是提供142Ω电阻到GND,为LVPECL输出提供直流偏置,并为GND提供直流电流路径。由于LVPECL输出共模电压为Vcc-1.3V,因此直流偏置电阻可以通过假设直流电流为14mA(R=Vcc-1.3V/14mA)来选择,导致Vcc-3.3V的R=142Ω。

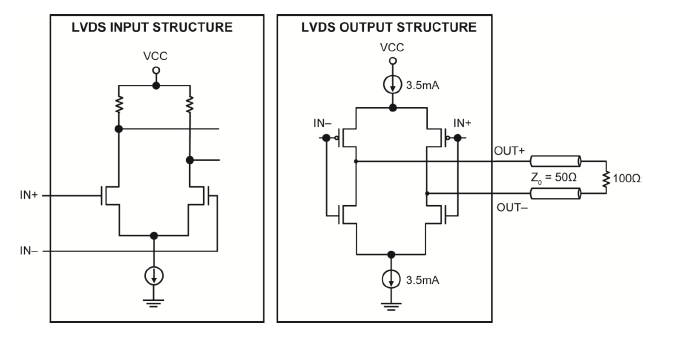

低压差分信号(LVDS)

低压差分信号(LVDS)输入需要在IN +和IN-引脚之间连接一个100Ω的电阻,共模电压约为1.2V。如果片内不包含100Ω的端接电阻,则必须包含在印刷电路板(PCB)上。

LVDS输出驱动器由3.5mA电流源组成,通过开关网络连接到差分输出OUT +和OUT-的输出引脚通常连接到差分传输线(Z0=100Ω)或单端传输线 (Z0=50Ω)用于阻抗匹配,通过接收器输入端的100Ω电阻端接导致LVDS逻辑的摆幅为350mV。

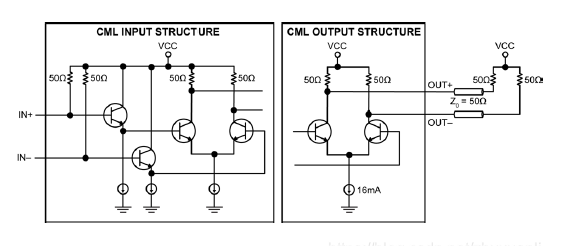

电流模式逻辑(CML)

大多数电流模式逻辑(CML)输入结构都有一个50Ω电阻连接到片内Vcc。如果没有,那么必须在PCB的IN +和IN-的两个输入端上施加一个电压。输入晶体管是射极跟随器,驱动差分对放大器。

CML输出由一对差分共发射极晶体管和50Ω集电极电阻组成,如上图所示的CML输出结构。OUT +和OUT-的输出通常连接到差分传输线(Z0=100Ω)或用于阻抗匹配的单端传输线(Z0=50Ω)。通过在共发射极差动BJT中切换电流来提供信号摆幅。假设电流源为16mA(典型值)并且CML输出用一个50Ω电阻上拉到Vcc,这个通过共模电压(Vcc-0.2V),输出电压从Vcc摆动到Vcc-0.4V。

高速电流控制逻辑

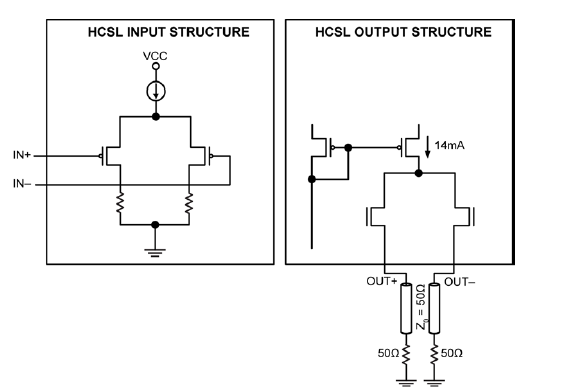

高速电流控制逻辑(HCSL)输入要求IN +和IN-的两个输入引脚上的单端摆幅为700mV,共模电压约为350mV。

典型的HCSL驱动器是具有开源输出的差分逻辑。其中每个输出引脚在0和14mA之间切换。当一个输出引脚为低电平(0)时,另一个输出引脚为高电平(驱动14mA)。OUT+引脚和OUT-引脚通常连接到差分传输线(Z0 =100Ω)或单端传输线(Z0 =50Ω),这需要一个外部端接电阻(50Ω到GND),从而为HCSL输入结构提供700mV的摆幅电平。