晶振低相噪low phase noise电路主要包括以下四个方面:

- 旁路电容器: 旁路电容器常用于除去相噪(noise)。它可以降低交流电源的阻抗使电路稳定工作,还可以吸电源线中的相噪。大多相噪问题可通过选择安装适宜常数的旁路电容器來解决。

- 旁路电容器容量: 通常使用的旁路电容器容量大致在0.01uF至0.1uF之间。电容器容量尽可能设定为较小的数值,且将晶振的电源电压Vcc、从接地线来看电源线的阻抗控制在晶振输岀频率约3倍的频带内。设定时应当确认电容的频率阻抗特性,防止高频侧或低频侧的阻抗增大。

- 旁路电容器的安装: 旁路电容器应尽可能安装在靠近晶振电源的地方。布线图案的距离越长寄生电感越大,高频侧的阻抗随之变大。布线应先连接旁路电容器后连接到电源线。这样,相噪必将通过旁路电容器,从而提高相噪去除效果。

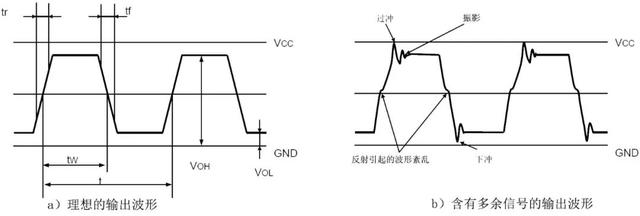

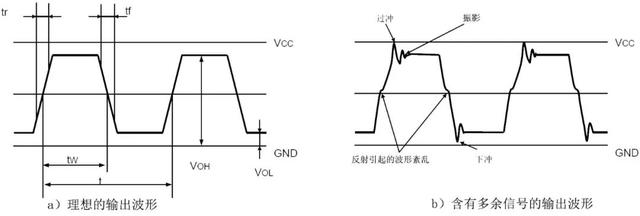

- 稳定的输岀线路:指能够把晶振输出波形(output wave)在不失真的情况下准确传输到输入对象的元器件,并能够尽可能减少相噪释放的线路。