2026年01月02日 08:07:14 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:9

晶振的一些参数并非固定值,大部分会随工作温度、杂散电容、激励功率等参数的变化而发生变化,在这种情况之下,合格的晶振会保持在正常频率范围内工作,不会造成芯片接收时钟信号的任何异常,但劣质不合格晶振则不同。

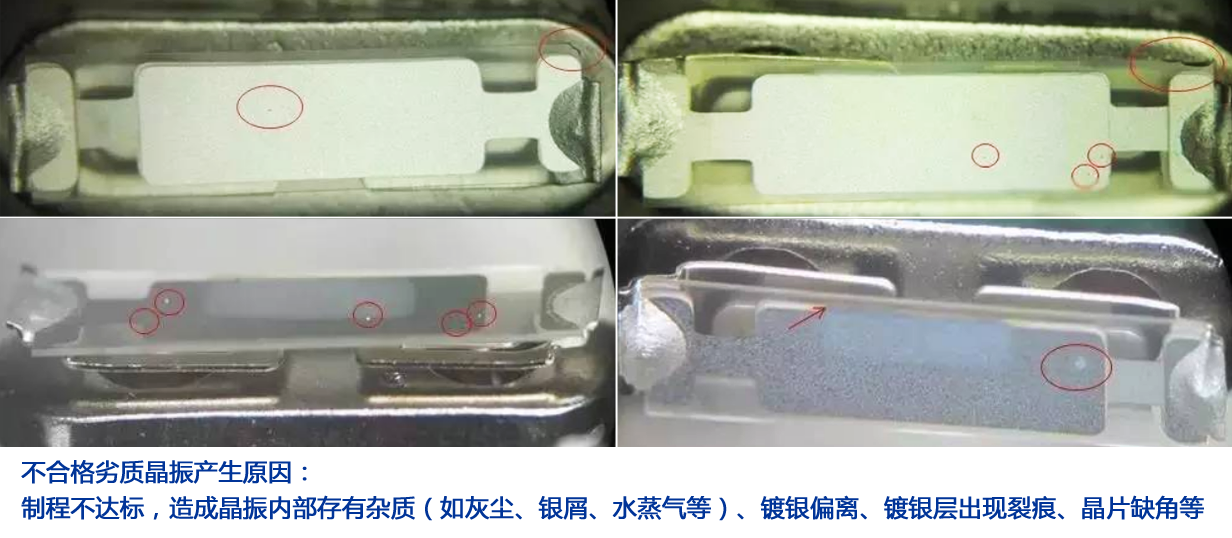

不合格劣质晶振产生原因:制程不达标,造成晶振内部存有杂质(如灰尘、银屑、水蒸气等)、镀银偏离、镀银层出现裂痕、石英晶片缺角等,不良品49S晶振解剖图所示如下(由高倍显微镜拍摄):

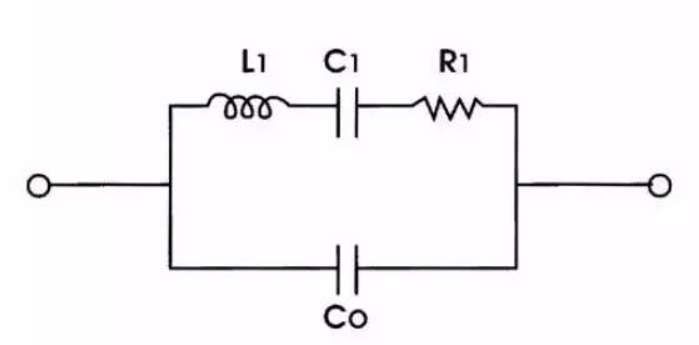

Equivalent Circuit of a Crystal Unit晶振等效电路图如下:

劣质不合格晶振参数异常主要体现在以下四点:

拓展阅读:晶振内部污染物的来源及对晶振性能的影响

晶振在长期使用过程中可能受到内部污染物的影响,导致频率漂移、稳定性下降甚至失效。其来源如下:

1、制造过程残留生产环境不洁净:切割、研磨或封装过程中可能引入微小颗粒(如石英碎屑、金属粉尘)。

2、封装密封不良:若气密性不足,外部污染物可能在制造阶段就已渗入。

3、使用环境影响

温湿度变化:高湿度环境可能导致水汽侵入,而温度剧烈波动可能加速材料老化。

化学腐蚀:暴露在含硫、氯等腐蚀性气体中,可能引发电极氧化。

机械应力:振动或冲击可能导致封装微裂纹,使污染物更易进入。

4、储存不当湿度过高或过低:建议储存湿度保持在 30%~75%RH,避免干燥或潮湿环境。

5、长期老化封装材料退化:长时间使用或热循环可能导致密封胶老化,形成微小裂缝,使污染物渗入。