2026年01月02日 08:16:21 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:9

有源晶振输出波形(LV)TTL,(H)CMOS,(P)ECL,LVDS,Clipped Sine Wave的主要区别如下:

通常,方波输出功率大,驱动能力强,但谐波分量丰富;正弦波带载能力不如方波,但谐波分量小。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。因为2.4V与5V之间有很大空闲,对改善噪声容限没好处,会增大系统功耗,并影响速度,所以后来出现LVTTL(Low Voltage TTL)。在晶振产品中,LVTTL分为3.3V、2.5V,其中以3.3V为主。

Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH> =3.5V;VIL<=1.5V。

CMOS相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。

使用时应注意:CMOS结构内部寄生有可控硅结构,当输入或输入管脚高于VCC一定值时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。

CMOS包括HCMOS与LVCMOS两类。LVCMOS属于低功耗设计。

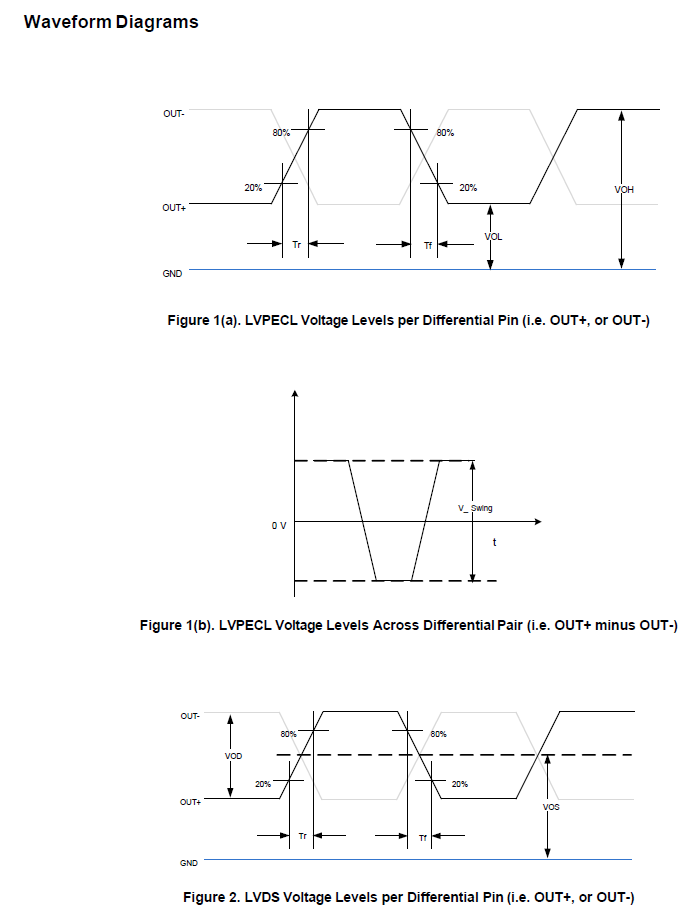

ECL电路的特点:基本门电路工作在非饱和状态,ECL电路具有相当高的速度,平均延迟时间可达几个毫微秒甚至亚毫微秒数量级。

ECL电路的逻辑摆幅较小(仅约 0.8V ,而 TTL 的逻辑摆幅约为 2.0V ),当电路从一种状态过渡到另一种状态时,对寄生电容的充放电时间将减少,这是 ECL电路具有高开关速度的重要原因。但逻辑摆幅小,对抗干扰能力不利。ECL电路具有很高的输入阻抗和低的输出阻抗。

Vcc=0V;Vee:-5.2V;VOH=-0.88V;VOL=-1.72V;VIH=-1.24V;VIL=-1.36V。 ECL电路速度快,驱动能力强,噪声小,很容易达到几百M的应用,但是功耗大,需要负电源。为简化电源,出现了PECL(ECL结构,改用正电压供电)和LVPECL。

削峰正弦波(Clipped Sine Wave)相比方波的谐波分量少很多,但驱动能力较弱,在负载10K//10PF时Vp-p为0.8Vmin。通常为TCXO温补晶振7050、5032、3225使用的波形。