2026年01月05日 09:32:56 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:8

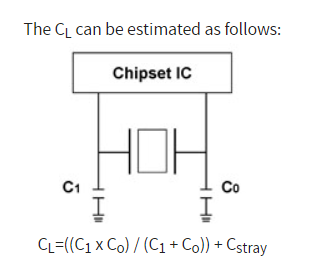

Cstray is the stray capacitance in the circuit, typically 3-5pF(as is supposed), and C1 and C0 are the external capacitors in the oscillator circuit. The CL in the circuit has to be as close to 16pF as possible to reach the specified output frequency. If the oscillation frequency is higher than specified, the capacitor values should be increased to lower the frequency. On the other hand, if the frequency is lower than specified, the capacitor values need to be decreased to raise the output frequency. When CL =16pF, C1 and C0 will be approximately 22-30pF each, plus the additional stray capacitance. The values of C1 and Co used in the circuit will have great effect on the CL which influences the output frequency.

上图中Cstray是电路中的杂散电容,一般为3~ 5pF (该数值因PCBA不同而异),C1 和C0 是振荡器电路的外部电容。电路中的CL 必须尽可能接近16pF才能达到指定的输出频率。如果振荡频率高于规定值,应增加电容值以降低频率。另一方面,如果频率低于规定值,则需要降低电容值以提高输出频率。当 CL=16 pF时,C1和C0各约22~30pF,再加上附加的杂散电容。电路中使用的C1和C0的值会对CL产生很大的影响,从而影响输出频率。

关于CL的定义

CL 代表负载电容。

负载电容被定义为在振荡器电路中从晶体的两个终端测量或计算出的总电容。晶体在振荡电路中组装时的输出频率是 CL 的函数。为了使石英晶体单元显示尽可能接近指定的输出频率,精确测量电路中的实际 CL 是非常重要的。