2026年01月07日 08:18:57 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:11

(无源晶振主要电气参数及其对电路的影响)

RR

阻抗RR越小,晶振越容易起振;反之,若晶振ESR过高,则晶振不易起振,可能会给电路造成不稳定。

C1

动态电容

L1

动态电感

C0

静电容

静电容C0不能太高,否则易产生较大的副波,影响晶振频率稳定性。

FL

在特定负载电容以及激励功率下,频偏越小越好。

DLD2

不同驱动功率(Drive Level)下,阻抗-阻抗最小,越小越好。

若晶振DLD2不良,会造成“睡眠晶振”,表现为晶振时振时不振。 晶振DLD2不良主要为晶振制程污染所导致。

DLD:英文全称Drive Level Dependency

指当不同功率驱动晶振时,所得阻抗与最小阻抗之差。DLD2越小越好。

当无源晶振制程受污染时,DLD2值会偏高,导致时振与时不振现象,即造成“睡眠晶振”(Crystal Sleeping)。

合格的晶振不会因驱动功率变化而变化而产生较高的阻抗差异。值得一提的是,目前一些晶振供应商不会主动提供此重要指标参数给客戶。

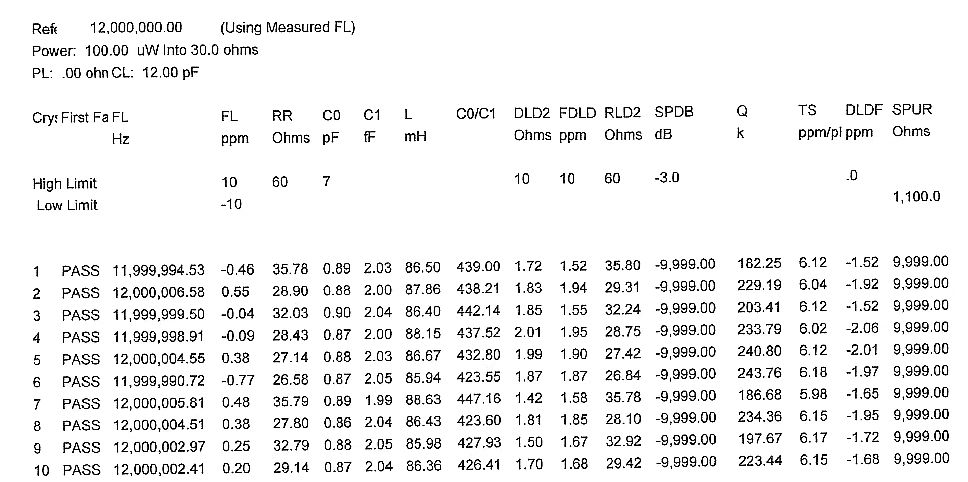

晶诺威科技产12MHz晶振合格品测试数据如下: