2026年01月09日 08:56:52 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:4

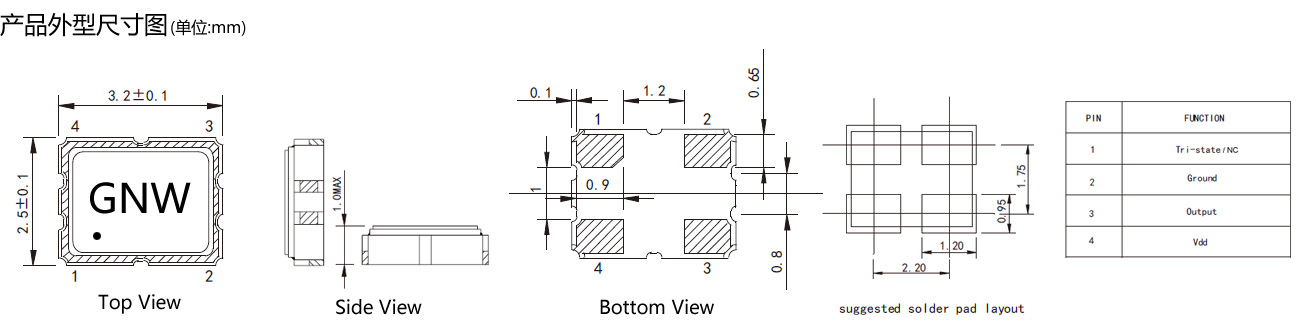

以晶诺威产SMD 3225贴片有源晶振(CMOS输出)为例:

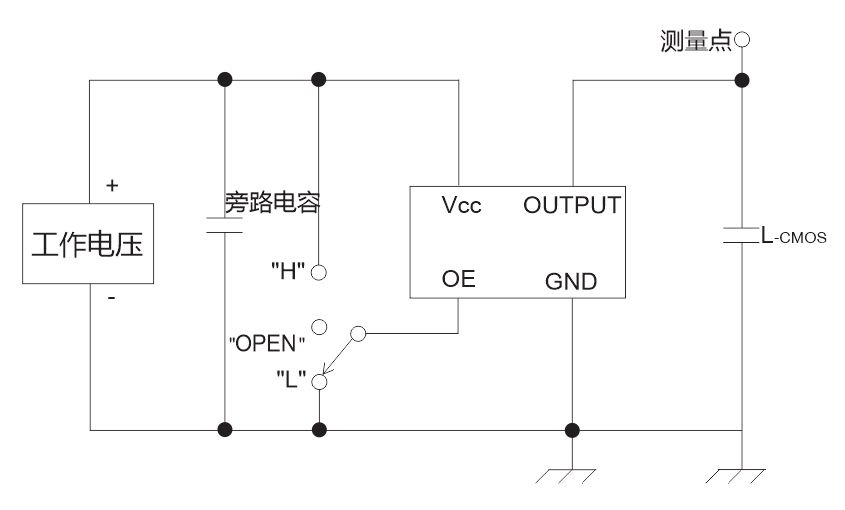

在电路设计焊接中,为了稳定运行,建议在Vdd和GND之间连接0.01μF至0.1μF的旁路电容,并尽可能靠近Vdd引脚。

(有源晶振测试电路)

关于有源晶振测试电路测试条件说明如下:

![]() 示波器

示波器

L_CMOS包括探头电容。

L_CMOS包括探头电容。

在靠近器件的Vdd和GND引脚之间应连接一个0.01μF至0.1μF的旁路(bypass)电容。

在靠近器件的Vdd和GND引脚之间应连接一个0.01μF至0.1μF的旁路(bypass)电容。

请使用低阻抗电流表。

请使用低阻抗电流表。

电源Power Supply

电源Power Supply