2026年01月10日 08:20:06 来源:深圳市晶诺威科技有限公司 >> 进入该公司展台 阅读量:28

有哪些因素影响无源晶振起振时间?

起振时间的长短主要由晶体的谐振电阻和振荡器的负性阻抗共同决定。高Q值的晶体谐振电阻较小,起振速度更快。晶诺威科技解释如下:

1、负载电容(CL)

如果负载电容很大,静态电容C0的改变对频率变化的影响很小,频率更加稳定。所以负载高,远端相位噪声好;若过大,则很难调整到标称频率,无源晶振起振慢。相反,如果负载电容较小,静电容C0的微小变化会造成频率的明显变化。近端相位噪声好,容易调整频率,晶振起振快。在选择晶体的负载电容时,我们要尽量权衡能量损耗和频率的稳定性。

2、阻抗(RR)

如果无源晶振阻抗过大,容易造成晶振起振困难,即:增加起振时间。

3、品质因素Q值

晶振的Q值称为“品质因数”。 Q值大,说明内阻小、损耗小、需要的激励功率小、起振快。

4、 DLD2

DLD: Drive Level Dependency

直译成中文为“驱动级别依赖性”。

DLD stands for Drive Level Dependence. The frequency and ESR (Equivalent Series Resistance) of a quartz crystal can be influenced by the drive level applied in an oscillation circuit to various degrees.

DLD 代表驱动器级别依赖性。石英晶体的频率和ESR(等效串联电阻)会受到振荡电路中施加的驱动电平的不同程度的影响。

DLD2越小越好,当晶振制程受污染时,则DLD2值会偏高,导致起振慢或时振时不振现象,即 “晶振休眠”。好的晶振不因驱动功率变化,而产生较高的阻抗差异,造成质量异常。晶振 DLD不良,集中反映在晶振使用过程的大多数不稳定状况。比如:用仪器测试是合格的,但使用时发现不能工作、加热或给一定外界激励后工作,但过一段时间后停止工作。

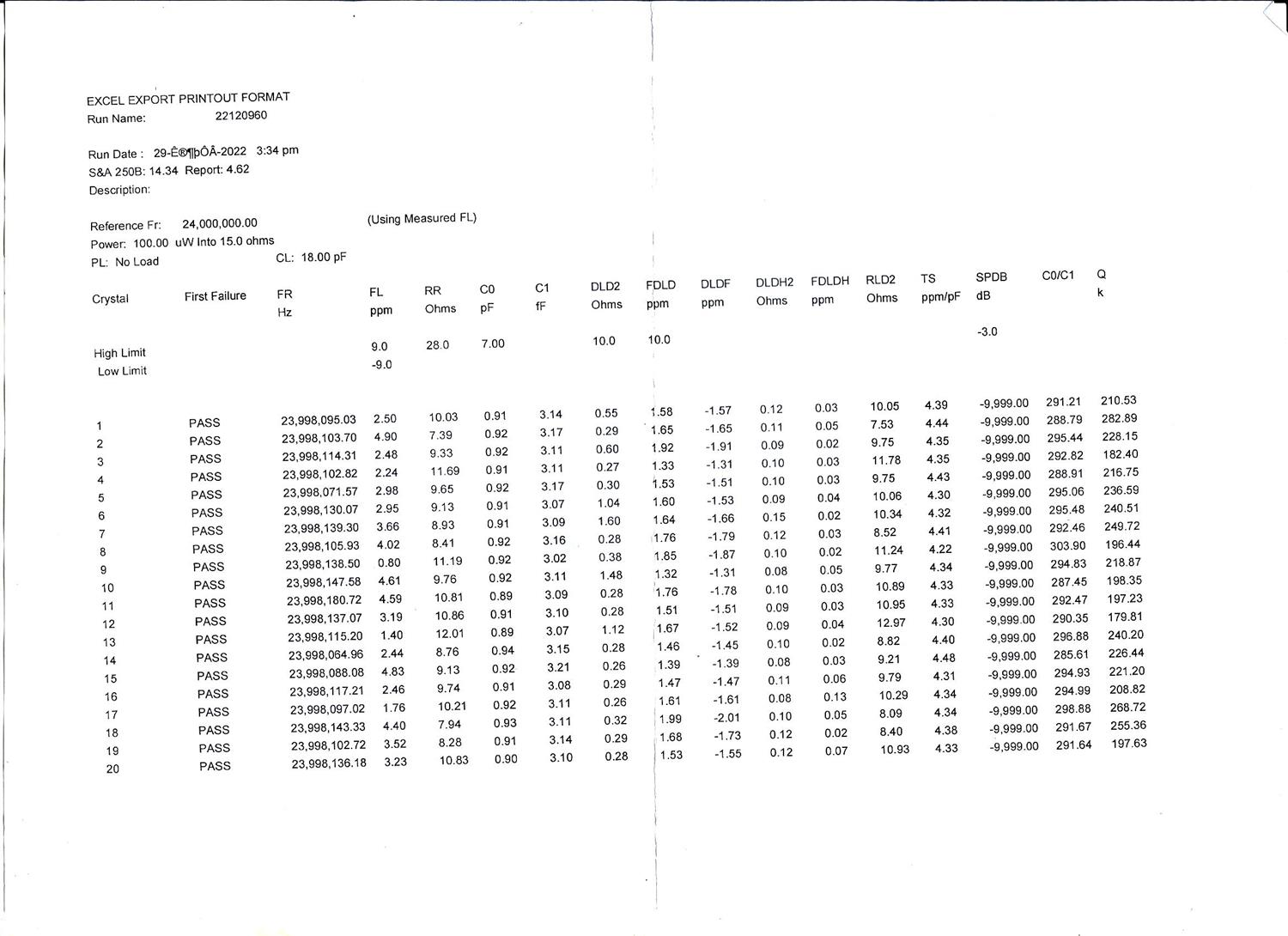

我司无源贴片晶振SMD3225 24MHz 18pF ±10ppm 电气参数测试数据如下: